## CONCEPTS IN RELIABLE AND OPTIMAL SYSTEMS DESIGNS

A Project Report

submitted by

#### **MOHAMMED SHOAIB**

in partial fulfilment of the requirements

for the award of the degree of

#### MASTER OF TECHNOLOGY

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY, MADRAS. MAY 2008

THESIS CERTIFICATE

This is to certify that the thesis titled CONCEPTS IN RELIABLE AND OPTIMAL

SYSTEMS DESIGN, submitted by Mohammed Shoaib, to the Indian Institute of Tech-

nology, Madras, for the award of the degree of Master of Technology, is a bona fide

record of the research work done by him under our supervision. The contents of this the-

sis, in full or in parts, have not been submitted to any other Institute or University for the

award of any degree or diploma.

Kamakoti. V

Research Guide

Assoc. Professor, Dept. of CSE

IIT Madras, Chennai 600 036

Srinivasan. S

Research Guide

Professor, Dept. of EE

IIT Madras, Chennai 600 036

Place: Chennai

Date: 01st May 2008

#### **ACKNOWLEDGEMENTS**

"One can pay back the loan of gold, but one dies forever in debt to those who are kind."

A Malay Proverb

I am thankful and beholden to God for his infinite mercy and blessings showered on me. I am superlatively saddled by my parents support, encouragement and prayers in making this all happen. My brother, Adnan, has been my single most important mentor, buddy and card-carrier throughout my five year stint at IIT Madras. I would like to acknowledge his help and thank him for all the wonderful discussions I had with him - every one of them was so important in reaching this milestone.

I am delighted to express my deepest sense of gratitude to Dr. Kamakoti, my advisor and guide at the Computer Science and Engineering (CSE) Department at IIT Madras. He kept me focused with his tremendous help, energy and motivation all through the wonderful year I spent at The Reconfigurable and Intelligent Systems Engineering (RISE) lab. The resources at the lab have been impeccable and I would like to thank him for helping me grow in such a world class facility. This overture would be left void if I equivocate the kind concern and guidance of Dr. Srinivasan, my co-advisor from the Electrical Engineering (EE) Department at IIT Madras. His forbearance has been phenomenal in carrying me along the various crests and troughs in my graduate career. In fact, the entire faculty at the EE department has been responsible for casting my foundation in VLSI and the CSE faculty has collectively been responsible for helping me build upon this strong foundation. Dr. Shankar, Dr. Debdeep and Dr. Ravindran have been instrumental in helping me look beyond the horizons of current technology. Their qualitative excellence and commitment to research has helped me transpire constructively and continue working on topics of significant importance.

This rubric would be incomplete without acknowledging the friendly support and enormous motivation from Noor, my closest pal at the RISE lab. His beneficial conatus has been pivotal in this work - technical and otherwise. I would like to thank him for

introducing me to evolutionary computing and helping me with various simulations, paper

writing, discussions and outages. Vimal, a third year undergraduate student in CSE at IIT

Madras has also been very helpful through various simulations and discussions. I grate-

fully acknowledge his contribution to this work and thank him for all the useful inputs. I

would like to thank my other lab mates - Venkat for his terrene and seraphic discussions

at the lab, Rajesh for his terrene discussions outside the lab and Chester for his seraphic

discussions within and outside the lab. I would also like to express my appreciation and

thanks to Kumar Dhirendra Pratap Singh Yadav from the EE department who has been a

wonderful companion and a good friend of mine at IIT Madras.

I cannot put in words, my expression of gratitude to the members of RISE lab at IIT

Madras for the numerous inputs, ideas and discussions, all of which were so very useful

in shaping up this work. Finally, I would like to mention significant motivation and fun-

times stocked up by my dorm mates - Saurabh, Nitin, Gaurav, Shashank, Lokesh and

Dhirendra. Their repose at restaurant lounges, movie theaters, gymnasiums and sports

grounds was something I'll have to thank for - a kinesis which was subservient to my

survival in research.

"What we have done for ourselves alone dies with us; what we have done for others and

the world remains and is immortal "- Albert Pike

SHOAIB, MOHAMMED

Indian Instt. of Tech. Madras

ii

#### **ABSTRACT**

KEYWORDS: Reliable Systems; Mathematical Optimization; Genetic Algorithms; Reconfigurable Hardware.

Designing reliable and optimal systems is one of the most challenging goals in contemporary electronics. As technologies scale and information processing gets critical, reliability in high performance systems plays a vital role in maintaining prolonged uptime and dependable outputs. In this work, we provide insights into designing reliable systems with optimal configurations using a popular stochastic technique called the Genetic Algorithm (GA). GAs are highly tunable algorithms which work with large amounts of data and simple operators to yield optimal solutions to difficult problems. The thesis uses abstractions at the transistor, gate and systems level to demonstrate the heuristics and challenges in the same. In a transistor optimization problem the thesis propounds a novel technique for evolving transistor net lists directly from truth table descriptions of arbitrary digital circuits. A salient feature of the proposed technique is the bypassing of gate level representation and optimization in the VLSI design flow. This leads to generation of custom and semi-custom library cells on the fly. The second problem involves finding input vector pairs that cause maximum power dissipation in digital circuits. A modified genetic search and a vector partitioning approach are used to obtain good lower bounds for the same. GA heuristics for FIR Filters are presented in a third problem. The thesis demonstrates that the filters thus designed are self-adaptive; respond to arbitrary frequency response landscapes; have built-in coefficient error tolerance capabilities; and have a minimal adaptation latency. As a byproduct of this, it also proposes a novel flow for the complete hardware design of what is termed as an Evolutionary System on Chip (ESoC). Finally a fourth optimization problem outlines the design methodology of a SEU tolerant Distributed RAM using Configurable Logic Blocks (CLBs) on FPGAs incorporating unused CLB BlockRAMs for high speed On-Chip memories and SEU resistant Tri-State Buffers (BUFTs) for the ECC.

## TABLE OF CONTENTS

| A               | CKNO  | <b>)WLEI</b> | DGEMENTS                                                                                                                                                                                                                                                                                                                                                                   | Ì                  |

|-----------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| A               | BSTR  | ACT          |                                                                                                                                                                                                                                                                                                                                                                            | iii                |

| L               | IST O | F TAB        | LES                                                                                                                                                                                                                                                                                                                                                                        | ix                 |

| LIST OF FIGURES |       |              |                                                                                                                                                                                                                                                                                                                                                                            |                    |

| A               | BBRE  | EVIATI       | ONS                                                                                                                                                                                                                                                                                                                                                                        | ix xiii xiii xv  1 |

| N               | OTAT  | ION          | ESixRESxiiNSxiiiDN AND BACKGROUND1Optimization Paradigms1onary Optimization2Genetic Algorithms: Principles of Natural Selection4A Basic GA Cycle5Representation $(\varphi)$ 6Variation $(v)$ 7Evaluation $(\varepsilon)$ 8Selection $(\zeta)$ 9gurable Hardware and Reliability10Logic Cell10Interconnect and Routing11Internal RAM11Errors in High Performance Memories12 |                    |

| 1               | MO    | TIVAT        | ION AND BACKGROUND                                                                                                                                                                                                                                                                                                                                                         | 1                  |

|                 | 1.1   | Design       | n Optimization Paradigms                                                                                                                                                                                                                                                                                                                                                   | 1                  |

|                 | 1.2   | Evolut       | tionary Optimization                                                                                                                                                                                                                                                                                                                                                       | 2                  |

|                 |       | 1.2.1        | Genetic Algorithms: Principles of Natural Selection                                                                                                                                                                                                                                                                                                                        | 4                  |

|                 |       | 1.2.2        | A Basic GA Cycle                                                                                                                                                                                                                                                                                                                                                           | 5                  |

|                 |       | 1.2.3        | Representation $(\varphi)$                                                                                                                                                                                                                                                                                                                                                 | 6                  |

|                 |       | 1.2.4        | Variation ( <i>v</i> )                                                                                                                                                                                                                                                                                                                                                     | 7                  |

|                 |       | 1.2.5        | Evaluation $(\varepsilon)$                                                                                                                                                                                                                                                                                                                                                 | 8                  |

|                 |       | 1.2.6        | Selection ( $\zeta$ )                                                                                                                                                                                                                                                                                                                                                      | 9                  |

|                 | 1.3   | Recon        | ifigurable Hardware and Reliability                                                                                                                                                                                                                                                                                                                                        | 10                 |

|                 |       | 1.3.1        | Logic Cell                                                                                                                                                                                                                                                                                                                                                                 | 10                 |

|                 |       | 1.3.2        | Interconnect and Routing                                                                                                                                                                                                                                                                                                                                                   | 11                 |

|                 |       | 1.3.3        | Internal RAM                                                                                                                                                                                                                                                                                                                                                               | 11                 |

|                 |       | 1.3.4        | Errors in High Performance Memories                                                                                                                                                                                                                                                                                                                                        | 12                 |

|                 | 1.4   | Conte        | xt and Objective                                                                                                                                                                                                                                                                                                                                                           | 13                 |

|                 | 1.5   | Organ        | ization of Thesis                                                                                                                                                                                                                                                                                                                                                          | 15                 |

| 2 | A G | ENETIC APPROACH TO GATELESS CUSTOM VLSI DESIGN FLOW | 16 |

|---|-----|-----------------------------------------------------|----|

|   | 2.1 | Introduction and Background                         | 16 |

|   | 2.2 | Genetic Topological Synthesis                       | 19 |

|   |     | 2.2.1 Representation and initial population         | 19 |

|   |     | 2.2.2 Variation: Crossover and Mutation             | 22 |

|   |     | 2.2.3 Selection and termination:                    | 23 |

|   | 2.3 | Experimental Results                                | 24 |

|   | 2.4 | Future Work                                         | 29 |

|   | 2.5 | Summary                                             | 30 |

| 3 | VEC | CTOR PARTITIONING AND GENETIC SEARCH METHODS FOR    |    |

|   |     | PE IN DIGITAL CIRCUITS                              | 32 |

|   | 3.1 | Prelude                                             | 32 |

|   |     | 3.1.1 Early estimation techniques                   | 32 |

|   | 3.2 | Handling the PDPE problem                           | 34 |

|   | 3.3 | 3 Previous Work                                     |    |

|   |     | 3.3.1 Contribution                                  | 36 |

|   | 3.4 | Algorithms for Power Virus Generation               | 37 |

|   |     | 3.4.1 Vector Partitioning                           | 38 |

|   |     | 3.4.2 Genetic Pattern Matching                      | 40 |

|   | 3.5 | Experimental Results                                | 43 |

|   | 3.6 | Summary                                             | 46 |

| 4 | HAI | RDWARE BASED GENETIC EVOLUTION OF FIR FILTERS       | 47 |

|   | 4.1 | Introduction                                        | 47 |

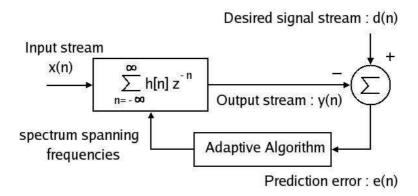

|   |     | 4.1.1 Adaptive Filters                              | 47 |

|   |     | 4.1.2 Some Approaches to FIR Filter Design          | 48 |

|   |     | 4.1.3 Genetic Operators from a new perspective      | 51 |

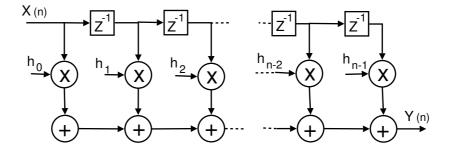

|   | 4.2 | FIR Architectures and Design                        | 52 |

|   |     | 4.2.1 FIR filter architectures                      | 52 |

|   |     | 4.2.2 Spatial and frequency domain design           | 53 |

|   | 4.3 | Evolutionary System Design                          | 54 |

|   | 4.4         | Intrinsic Design                                                  |  |  |  |  |  |  |  |

|---|-------------|-------------------------------------------------------------------|--|--|--|--|--|--|--|

|   |             | 4.4.1 The Evolutionary System on Chip (ESoC):                     |  |  |  |  |  |  |  |

|   | 4.5         | Experimental results                                              |  |  |  |  |  |  |  |

|   | 4.6         | Summary                                                           |  |  |  |  |  |  |  |

| 5 |             | EU TOLERANT DISTRIBUTED CLB RAM FOR IN-CIRCUIT RE-<br>NFIGURATION |  |  |  |  |  |  |  |

|   | 5.1         | SEUs and FPGAs                                                    |  |  |  |  |  |  |  |

|   | 5.2         | Distributed CLB RAMs                                              |  |  |  |  |  |  |  |

|   | 5.3         | Fault Tolerant DRAM                                               |  |  |  |  |  |  |  |

|   | 5.4         | Application: In-Circuit Reconfiguration                           |  |  |  |  |  |  |  |

|   |             | 5.4.1 Design Specifics                                            |  |  |  |  |  |  |  |

|   | 5.5         | Experimental Results                                              |  |  |  |  |  |  |  |

|   | 5.6         | Future Work                                                       |  |  |  |  |  |  |  |

|   | 5.7         | Summary                                                           |  |  |  |  |  |  |  |

| 6 | EPI         | <b>EPILOGUE</b>                                                   |  |  |  |  |  |  |  |

|   | 6.1         | Wrap Up                                                           |  |  |  |  |  |  |  |

|   | 6.2         | Conclusions                                                       |  |  |  |  |  |  |  |

|   | 6.3         | Future Work                                                       |  |  |  |  |  |  |  |

| A | CM          | CMOS LOGIC DESIGN AND THE IRSIM SIMULATOR                         |  |  |  |  |  |  |  |

|   | <b>A.</b> 1 | Digital CMOS Logic Design                                         |  |  |  |  |  |  |  |

|   |             | A.1.1 Static CMOS Logic Design                                    |  |  |  |  |  |  |  |

|   |             | A.1.2 Dynamic CMOS Logic Design                                   |  |  |  |  |  |  |  |

|   | A.2         | The IRSIM Switch Level Simulator                                  |  |  |  |  |  |  |  |

|   | A.3         | Modeling details                                                  |  |  |  |  |  |  |  |

| В |             | E ESTIMATES USING THE GENETIC SEARCH AND PARTITION-METHODS        |  |  |  |  |  |  |  |

|   | <b>B</b> .1 | Modified Genetic Search Method                                    |  |  |  |  |  |  |  |

|   |             | B.1.1 Results for the Zero Delay Model                            |  |  |  |  |  |  |  |

|   |             | B 1.2 Results for the Unit Delay Model                            |  |  |  |  |  |  |  |

|   | B.2         | Vector Partitioning Method, Zero Delay | 107 |

|---|-------------|----------------------------------------|-----|

| C | HAI         | MMING CODE AND ECC                     | 111 |

|   | <b>C</b> .1 | Error Correcting Codes(ECC)            | 111 |

|   | <b>C.2</b>  | Hamming Codes                          | 111 |

|   | C.3         | Block sizes for the Hamming Code       | 114 |

## LIST OF TABLES

| 2.1         | Gene structure in a chromosome using .sim encoding                                                                 | 19  |

|-------------|--------------------------------------------------------------------------------------------------------------------|-----|

| 2.2         | A model .sim file for the circuit example in Fig.2.3                                                               | 20  |

| 2.3         | Exemplary Circuit results for test truth table inputs with the mutation and elitism rate over multiple generations | 31  |

| 3.1         | ISCAS'85 Benchmark suite specifications                                                                            | 45  |

| 3.2         | Comparison of PDPE for ISCAS'85 Combinational Benchmark Circuits - Zero Delay Model                                | 45  |

| 4.1         | Coefficient sets for filter test cases                                                                             | 73  |

| 4.2         | Coefficient evolution results over mac/mic generation                                                              | 73  |

| 5.1         | Test cases with variable data word lengths for 1KB ftDRAM on Xilinx Virtex II XC2VP2-7FG256 Device                 | 87  |

| 5.2         | Test cases for variable memory sizes with and without error checks                                                 | 87  |

| <b>A.</b> 1 | An example of a .sim file for the IRSIM simulator                                                                  | 99  |

| B.1         | Power virus vectors and genetic search progression - zero delay model for the ISCAS'85 benchmark circuits          | 100 |

| B.1         | Power virus vectors and genetic search progression - zero delay model for the ISCAS'85 benchmark circuits          | 101 |

| B.1         | Power virus vectors and genetic search progression - zero delay model for the ISCAS'85 benchmark circuits          | 102 |

| B.1         | Power virus vectors and genetic search progression - zero delay model for the ISCAS'85 benchmark circuits          | 103 |

| B.2         | Power virus vectors and genetic search progression - unit delay model for the ISCAS'85 benchmark circuits          | 104 |

| B.2         | Power virus vectors and genetic search progression - unit delay model for the ISCAS'85 benchmark circuits          | 105 |

| B.2         | Power virus vectors and genetic search progression - unit delay model for the ISCAS'85 benchmark circuits          | 106 |

| <b>B</b> .2 | Power virus vectors and genetic search progression - unit delay model for the ISCAS'85 benchmark circuits | 107 |

|-------------|-----------------------------------------------------------------------------------------------------------|-----|

| B.3         | Power virus vectors and partitioning iteration - zero delay model for the ISCAS'85 benchmark circuits     | 107 |

| B.3         | Power virus vectors and partitioning iteration - zero delay model for the ISCAS'85 benchmark circuits     | 108 |

| B.3         | Power virus vectors and partitioning iteration - zero delay model for the ISCAS'85 benchmark circuits     | 109 |

| B.3         | Power virus vectors and partitioning iteration - zero delay model for the ISCAS'85 benchmark circuits     | 110 |

| <b>C</b> .1 | Parity Checks for the first 17 bits of the Hamming code                                                   | 112 |

| C.2         | Parity Check Example for a 7 bit data word                                                                | 113 |

| C.3         | Single Error detection using the Hamming ECC                                                              | 113 |

| <b>C</b> .4 | Hamming ECC block sizes                                                                                   | 114 |

## LIST OF FIGURES

| 1.1  | Evolutionary hardware synthesis - Intrinsic and Extrinsic                                                                                    | ۷  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | A basic GA cycle                                                                                                                             | 5  |

| 1.3  | IP representation using directed and undirected graphs                                                                                       | 7  |

| 1.4  | A typical FPGA Logic Cell                                                                                                                    | 11 |

| 1.5  | The thesis framework - optimization abstractions                                                                                             | 14 |

| 2.1  | Custom design flow simplification using the proposed genetic method - Elimination of the boolean optimization step.                          | 18 |

| 2.2  | Initial population generation with the corresponding transistor topology and SFG for the netlist                                             | 20 |

| 2.3  | Dynamic CMOS simulation circuit example                                                                                                      | 21 |

| 2.4  | Circuit to chromosome translation                                                                                                            | 21 |

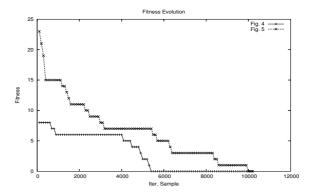

| 2.5  | The fitness evolution samples over intermediate generations, plotted for cases in Fig.2.6 and Fig.2.7 with four and five inputs respectively | 24 |

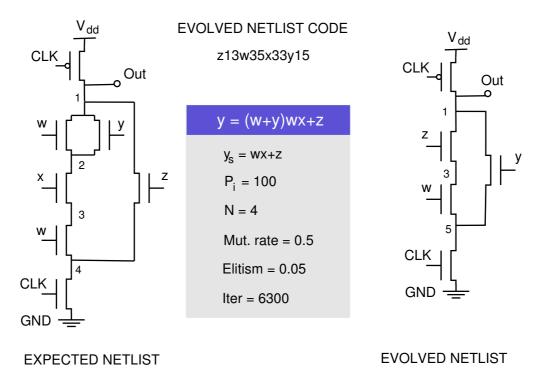

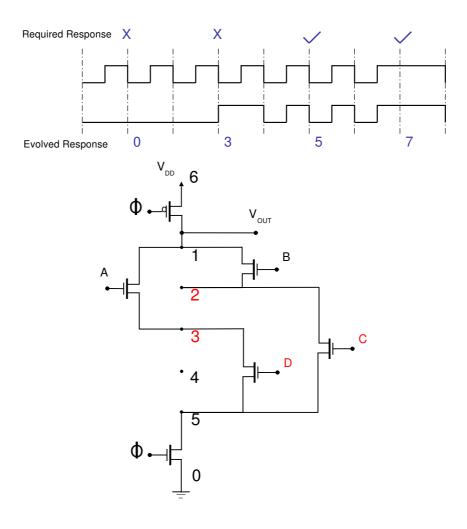

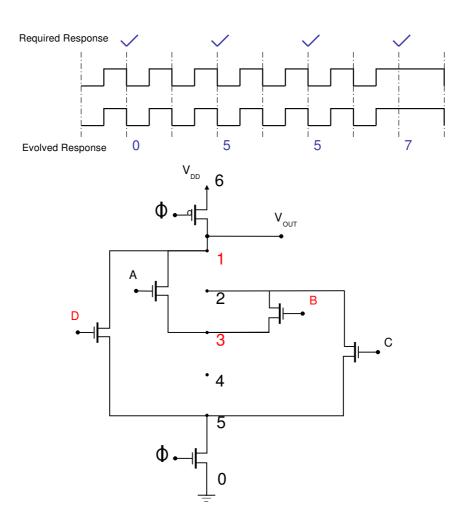

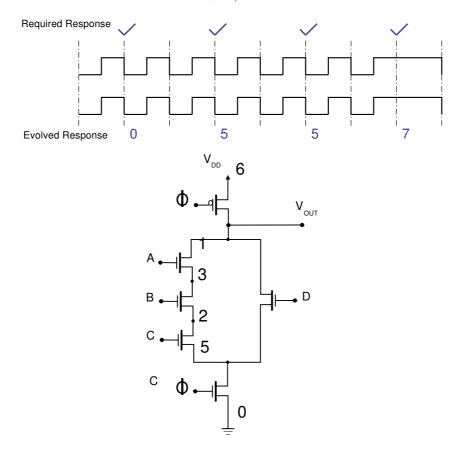

| 2.6  | Evolved SPICE netlist for the test case 1                                                                                                    | 25 |

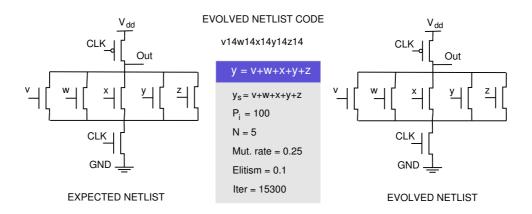

| 2.7  | Evolved SPICE netlist for the test case 2                                                                                                    | 25 |

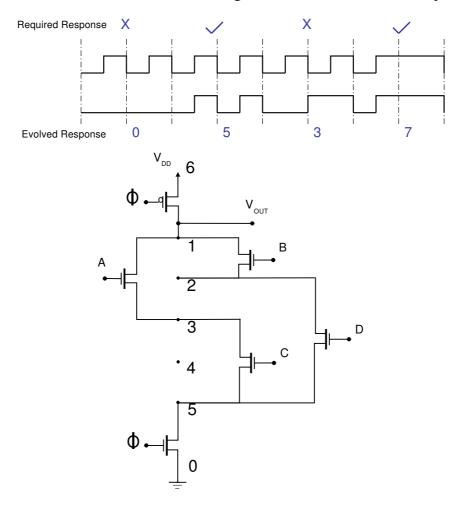

| 2.8  | Evolving transistor netlist: function AC+BD                                                                                                  | 26 |

| 2.9  | Evolving transistor netlist: function AD+BC                                                                                                  | 27 |

| 2.10 | Evolving transistor netlist for example function ABC+D                                                                                       | 28 |

| 2.11 | Final evolved transistor netlist - ABC+D                                                                                                     | 29 |

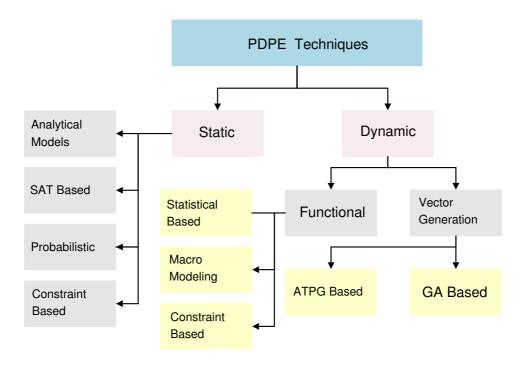

| 3.1  | PDPE Techniques in digital VLSI design                                                                                                       | 33 |

| 3.2  | Vector partitioning the PV                                                                                                                   | 38 |

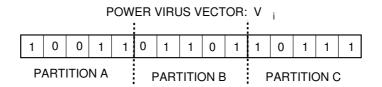

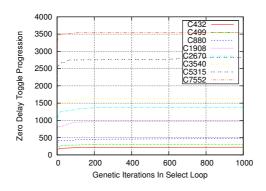

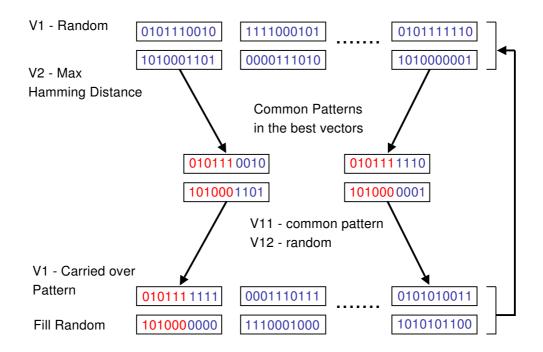

| 3.3  | Modified Genetic Method zero delay toggle progression                                                                                        | 40 |

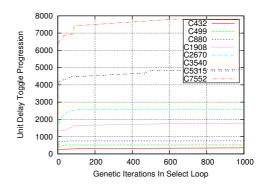

| 3.4  | Modified Genetic Method unit delay toggle progression                                                                                        | 40 |

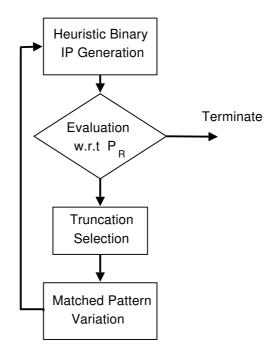

| 3.5  | Genetic Search methodology for PDPE in digital circuits                                                                                      | 43 |

| 3.6  | Genetic Search algorithm for the PDPE problem                                                                                                | 44 |

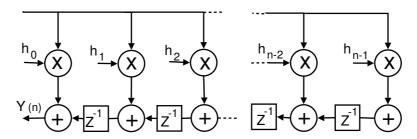

| 4.1  | as a feed                                                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------|

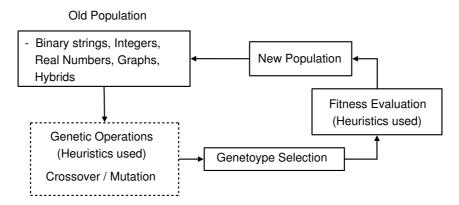

| 4.2  | A Generic GA Cycle - Involves four major steps Initial Population Generation, Variation, Evaluation and Selection |

| 4.3  | Direct form implementation of digital FIR filters                                                                 |

| 4.4  | Transposed direct form implementation of digital FIR filters                                                      |

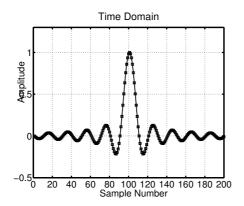

| 4.5  | Sinc function expressed as $f(x)=\sin(x)/x$ and its transform, a window function                                  |

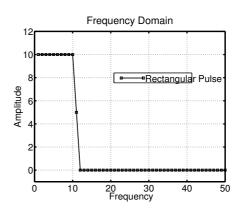

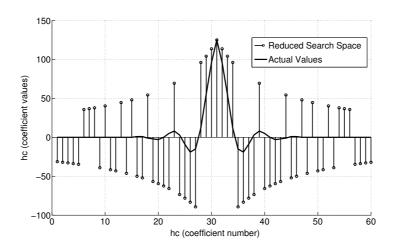

| 4.6  | Reduced GA search space with the Gaussian switch                                                                  |

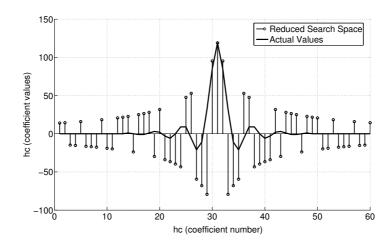

| 4.7  | Sample case with a lower cut-off frequency                                                                        |

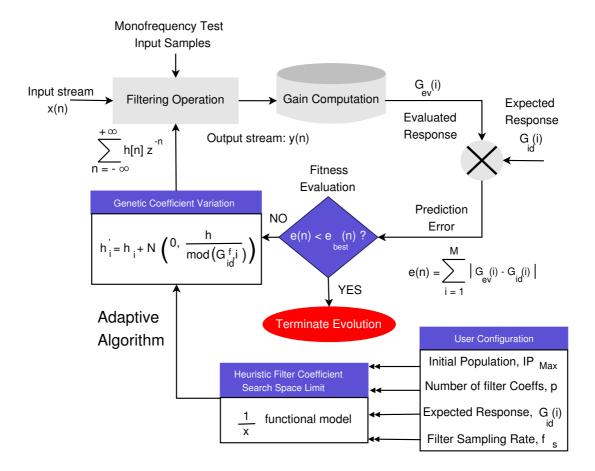

| 4.8  | The evolutionary adaptive filter design including the UI                                                          |

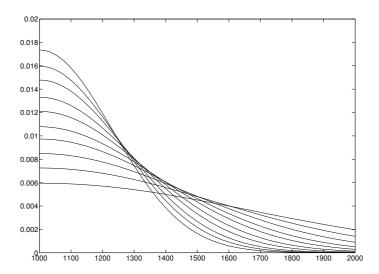

| 4.9  | Decreasing $\sigma$ with increasing coefficient numbers $j$ in the normal random mutation                         |

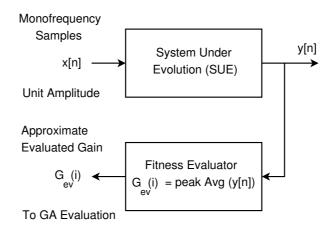

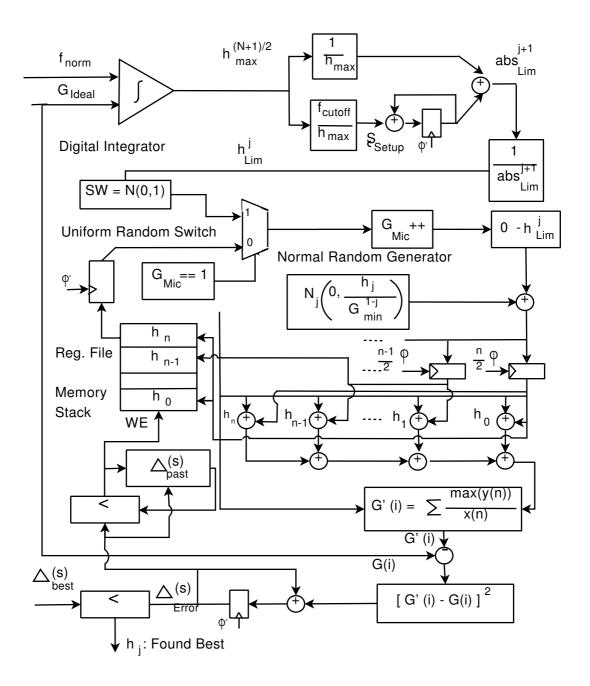

| 4.10 | The fitness evaluator for the system under evolution                                                              |

| 4.11 | Macro-Evolutionary System on Chip                                                                                 |

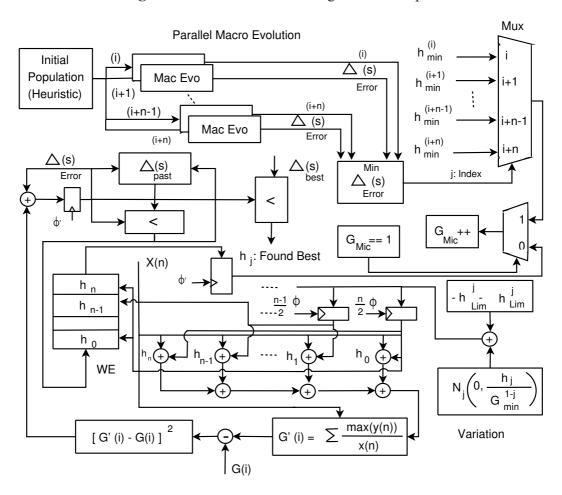

| 4.12 | Parallel and Scalable Micro-Evolution Stage                                                                       |

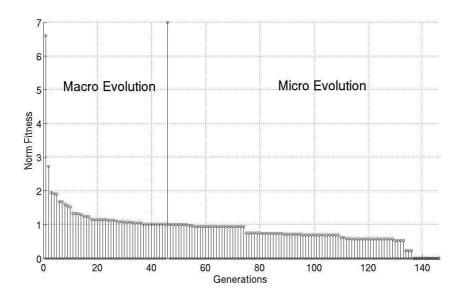

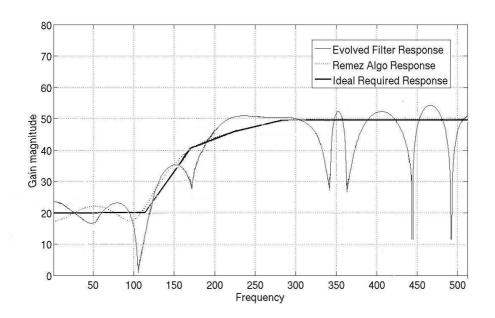

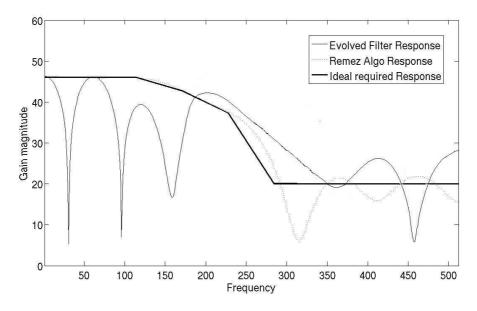

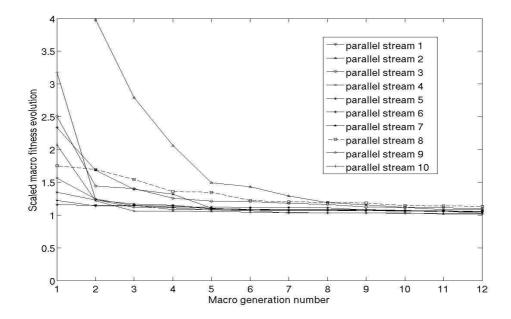

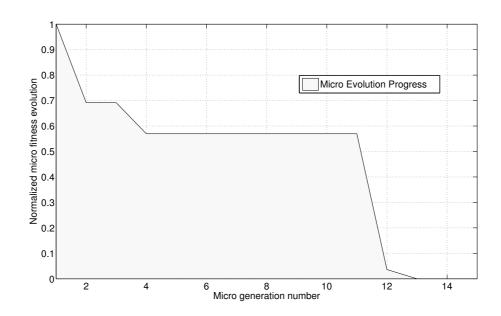

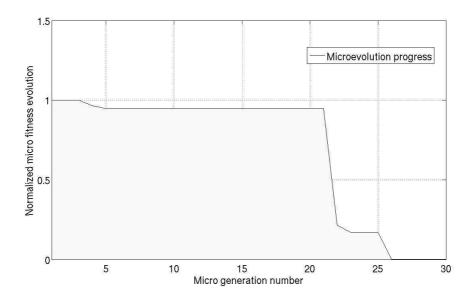

| 4.13 | Macro and micro fitness evolution progress - case 1                                                               |

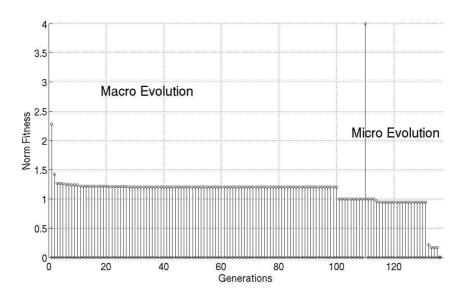

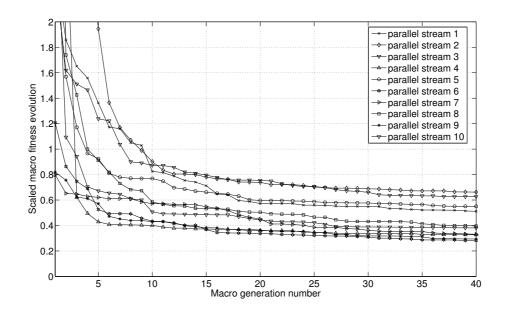

| 4.14 | Macro and micro fitness evolution progress - coarser case                                                         |

| 4.15 | Frequency response evolution progress - HPF case                                                                  |

| 4.16 | Macro fitness evolution progress - HPF case                                                                       |

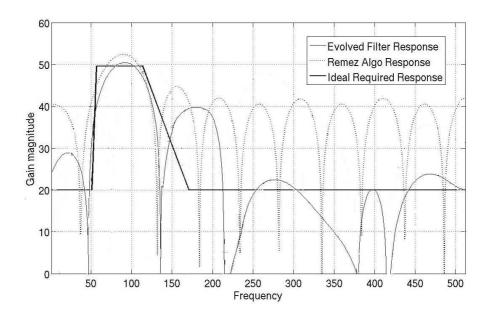

| 4.17 | Frequency response evolution progress - BPF case                                                                  |

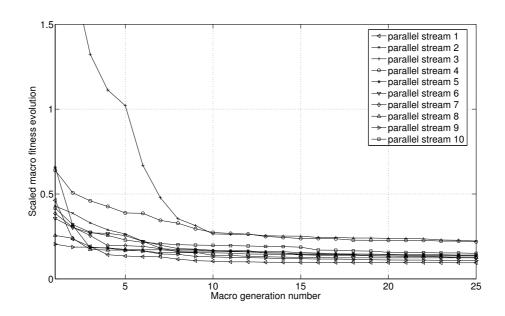

| 4.18 | Macro fitness evolution progress - BPF case                                                                       |

| 4.19 | Frequency response evolution progress - LPF case                                                                  |

| 4.20 | Macro fitness evolution progress - LPF case                                                                       |

| 4.21 | Macro fitness evolution progress - case 1                                                                         |

| 4.22 | Macro fitness evolution progress - case 2                                                                         |

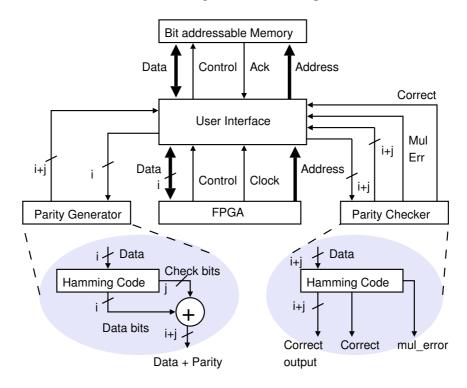

| 5.1  | The Proposed Hamming ECC Fault Tolerant DRAM Memory Model                                                         |

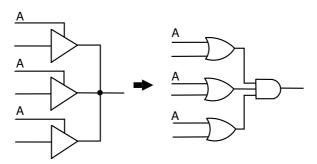

| 5.2  | The Virtex Tri-State Buffers: Equivalent to Wired AND-OR Logic                                                    |

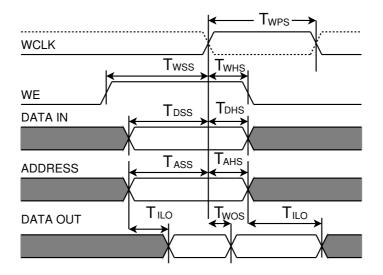

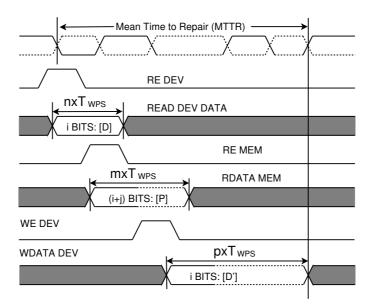

| 5.3  | The DRAM ECC Cycle Clock Timing Diagram                                                                           |

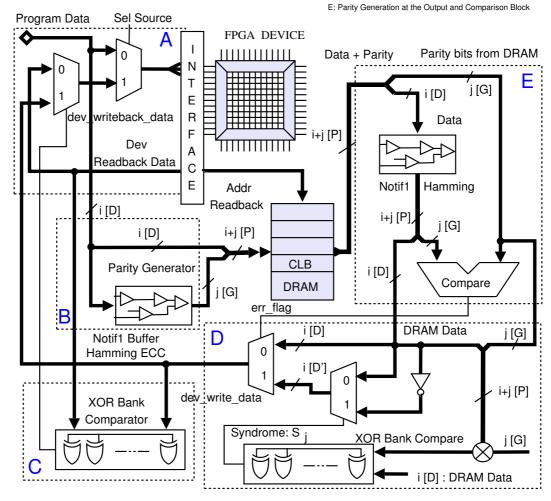

| 5.4  | The In-Circuit reconfiguration methodology using the ftDRAM                                                       |

| 5.5  | The In-circuit Reconfiguration Timing Diagram.                                                                    |

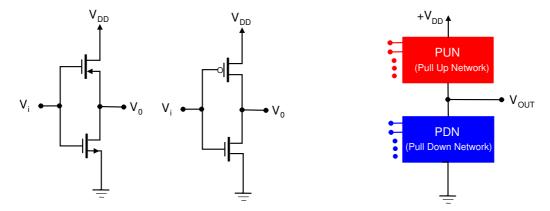

| <b>A.</b> 1 | Static inverter using different n and p transistor representations | 94 |

|-------------|--------------------------------------------------------------------|----|

| A.2         | Pull up-down networks in the static inverter                       | 94 |

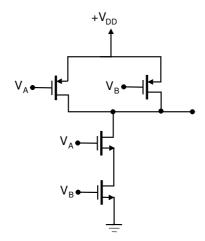

| A.3         | Static CMOS NAND                                                   | 95 |

| A.4         | Truth table for NAND                                               | 95 |

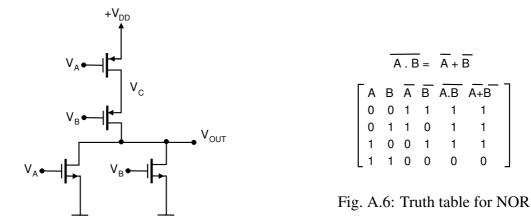

| A.5         | Static CMOS NOR circuit                                            | 96 |

| A.6         | Truth table for NOR                                                | 96 |

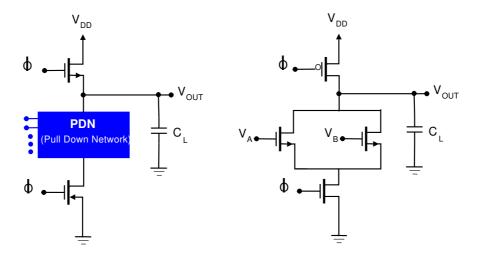

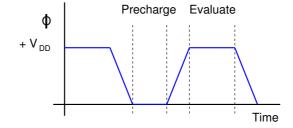

| <b>A.</b> 7 | Dynamic CMOS PDN                                                   | 97 |

| A.8         | Dynamic CMOS Clock                                                 | 97 |

#### **ABBREVIATIONS**

**ANN** Artificial Neural Network

**ATG** Automatic Test Generation

**ASIC** Application Specific Integrated Circuit

**BiET** Built-in Error Tolerance

**BUFT** Tristate Buffer

**CHE** Complete Hardware Evolution

**CLB** Configurable Logic Block

**CRF** Coeffficient Register File

**CROOT** Cone Root

**DRAM** Distributed Random Access Memory

**DSP** Digital Signal Processing

**DWC** Doubling With Comparison

**ECC** Error Correction Control

**ECC** Error Correcting Codes

**ER** Elitism Rate

**ESoC** Evolutionary System-on-Chip

**FD** Frequency Domain

**FIR** Finite Impulse Response

**FPGA** Field Programmable Gate Array

ftDRAM fault tolerant Distributed Random Access Memory

**FWL** Finite Word Length

**GA** Genetic Algorithm

**GO** Genetic Operator

**HD** Hamming Distance

IC Integrated Circuit

IR Incircuit Reconfiguration

**IIR** Infinite Impulse Response

**IP** Initial Population

JTAG Joint Test Action Group

LL Label List

**LUT** Look-Up-Table

MBU Multiple Bit Upset

MEU Multiple Event Upset

MOS Metal Oxide Semiconductor

MR Mutation Rate

MTTR Mean Time To Repair

NDS Non-Dominated Set

**NoC** Network on Chip

**PDPE** Peak Dynamic Power Estimation

PI Primary Inputs

**PO** Primary Outputs

**PODG** Primitive Operator Directed Graph

**PoS** Product of Sum

**RAM** Random Access Memory

**SA** Simulated Annealing

SD Spatial Domain

**SEB** Single Event Burnout

**SEE** Single Event Effect

**SEGR** Single Event Gate Rupture

**SET** Single Event Transient

**SEU** Single Event Upset

SHE Single Hard Error

**SoP** Sum of Product

**SRAM** Static Random Access Memory

**TMR** Triple Modular Redundancy

TTM Time-to-Market

**WE** Write Enable

## **NOTATION**

| C                                 | T                                                     |

|-----------------------------------|-------------------------------------------------------|

| $S_{j}$                           | Input signal and gate node of the $j^{th}$ transistor |

| $n_{j}^{1}$                       | Source node of the $j^{th}$ transistor                |

| $S_j \\ n_j^1 \\ n_j^2 \\ T_{ij}$ | Drain node of the $j^{th}$ transistor                 |

| $T_{ij}$                          | Transistor type (CMOS/NMOS) between nodes $i$ and $j$ |

| $L(W)_{ij}$ $R_{ij}$              | Transistor channel length (width) in $\mu$ m          |

| $R_{ij}$                          | Uniform Random Selector                               |

| $\delta_{ij}$                     | Select Scalar for the GA                              |

| $rac{\xi}{arepsilon}$            | Genetic copy operator                                 |

|                                   | Genetic fitness evaluator                             |

| l                                 | Length of truth table input                           |

| $f_i$                             | $i^{th}$ chromosome fitness in genotype matrix        |

| $\oplus$                          | Logical XOR operator                                  |

| Λ                                 | Fitness sorting operator                              |

| $C_g$                             | Output capacitance of gate g                          |

| $V_{dd}$                          | Rail supply voltage                                   |

| $P_R$                             | Energy per clock cycle (peak power)                   |

| O                                 | Complexity order of an algorithm                      |

| $\bigcup$                         | Set union operator                                    |

| $(v_i, v_j) \approx$              | Random input vector pair to circuit                   |

| $\simeq$                          | Asymptotically equal to                               |

| $h_i$                             | $i^{th}$ filter coefficient (tap weight)              |

| $rac{\delta_p}{\delta_s}$        | Filter passband ripple                                |

|                                   | Filter stopband ripple                                |

| $\Delta F$                        | Filter transition bandwidth                           |

| $G_{id(ev)}$                      | Filter ideal (evaluated) response                     |

| $f_n$                             | Filter normalized frequency - $\frac{f}{f_s}$         |

| $f_s$                             | Filter sampling frequency                             |

| $f_c I f_{cutoff}$                | Filter cutoff frequencies                             |

| $f_{Nyq}$                         | Filter nyquist frequency                              |

| $\Delta^{mean}$                   | Mean inverse coefficient space value                  |

| $\delta^{step}$                   | Inverse coefficient space step for interpolation      |

| $N(\mu, \sigma)$                  | Std normal distribution - mean $\mu$ & SD $\sigma$    |

| $\xi_{curr}$                      | Current evaluated fitness operator                    |

| :                                 | Matrix concatenation operator                         |

| •                                 | Vector dot product                                    |

| $\phi$                            | Circuit clock signal                                  |

| $T_{WCLK(H)}$                     | Clock write (hold) period                             |

|                                   |                                                       |

#### **CHAPTER 1**

#### MOTIVATION AND BACKGROUND

Typical engineering systems are described by a very large number of variables, and it is the designer's task to specify appropriate values for these variables. Skilled designers utilize their knowledge, experience, and judgment to specify these and design effective engineering systems. Because of the size and complexity of the typical design task, however, even the most skilled designers are unable to take into account all of the variables simultaneously. Design optimization is the application of numerical algorithms and techniques to engineering systems to assist in improving the system's performance, reliability, and cost [Adoptech (2008)]. Optimization methodologies can be applied during the development stage to ensure that the finished designs will have high performance, reliability and low cost. Alternatively, optimization methods can be applied to existing designs to identify potential improvements. This thesis is dedicated to providing the tools and knowledge required to generate practical designs that are useful in the real world. It demonstrates the use of a probabilistic algorithm called the Genetic Algorithm (GA) for the same. The thesis also presents insights into reliability concepts on a reconfigurable platform.

## 1.1 Design Optimization Paradigms

Optimization refers to the study of problems in which one seeks to minimize or maximize a real function by systematically choosing the values of real or integer variables from within an allowed set. An optimization problem can be represented as follows

Given: A function

$$f: A \rightarrow R$$

from some set A to the real numbers (1.1)

Find: An element

$$x_0$$

in A such that (1.2)

$$f(x_0) \le f(x) \ \forall \ x \in A \ ("minimization") \tag{1.3}$$

$$f(x_0) \ge f(x) \, \forall \, x \in A \, ("maximization")$$

(1.4)

In Eq.(1.2) through Eq.(1.4), typically, A is some subset of the Euclidean space  $R_n$ , often specified by a set of constraints, equalities or inequalities that the members of A have to satisfy. The domain A of f is called the search space, while the elements of A are called candidate solutions or feasible solutions. The function f is called an objective function, or cost function. A feasible solution that minimizes (or maximizes, if that is the goal) the objective function is called an optimal solution.

Many real-world and theoretical problems may be modeled in this general framework. Sometimes this technique is referred to as energy minimization wherein the concept is the association of the function f with the energy of a system. Generally, when the feasible region or the objective function of the problem does not present convexity, there may be several local minima and maxima, where a local minimum  $x^*$  is defined as a point for which there exists some  $\delta>0$  so that for all x such that  $||x-x^*|| \leq \delta$ , the expression  $f(x^*) \leq f(x)$  holds; that is to say, on some region around  $x^*$  all of the function values are greater than or equal to the value at that point. Local maxima are defined similarly.

A large number of algorithms proposed for solving non-convex problems including the majority of commercially available solvers are not capable of making a distinction between local optimal solutions and rigorous optimal solutions, and will treat the former as actual solutions to the original problem [Optimization (2008)]. The branch of applied mathematics and numerical analysis that is concerned with the development of deterministic algorithms that are capable of guaranteeing convergence in finite time to the actual optimal solution of a non-convex problem is called global optimization. The local and global optimization concepts are critical in problem validation. The evolutionary heuristics using GAs proposed in this thesis provide insights into both of these using three different problems.

## 1.2 Evolutionary Optimization

Why use evolution as an inspiration for solving computational problems?

The mechanisms of evolution seem well suited for some of the most pressing computational problems in many fields. Many computational problems require searching through a huge number of possibilities for solutions. On an alternative note, search problems can often benefit from an effective use of parallelism, in which many different possibilities are explored simultaneously in an efficient way. But what is needed is both computational parallelism (i.e., many processors evaluating sequences at the same time) and an intelligent strategy for choosing the next set of sequences to evaluate.

Many computational problems require a computer program to be adaptive - to continue to perform well in a changing environment. Others require computer programs to be innovative - to construct something truly new and original. Finally, many computational problems require complex solutions that are difficult to program by hand. In the current context, the best route to intelligence is through a bottom-up paradigm in which humans write only very simple rules, and complex behaviors emerge from the massively parallel application and interaction of these simple rules.

In evolutionary computation the rules are based on natural selection with variation due to crossover and/or mutation; the hoped-for emergent behavior is the design of highquality solutions to difficult problems and the ability to adapt these solutions in the face of a changing environment. Biological evolution is an appealing source of inspiration for addressing these problems. Evolution is, in effect, a method of searching among an enormous number of possibilities for solutions. In biology the enormous set of possibilities is the set of possible genetic sequences, and the desired solutions are highly fit organisms organisms well able to survive and reproduce in their environments. Evolution can also be seen as a method for designing innovative solutions to complex problems. Seen in this light, the mechanisms of evolution can inspire computational search methods. Of course the fitness of a biological organism depends on many factors - for example, how well it can weather the physical characteristics of its environment and how well it can compete with or cooperate with the other organisms around it. The fitness criteria continually change as creatures evolve as typified by the FIR filter problem in Chap.4. So evolution is searching a constantly changing set of possibilities. Searching for solutions in the face of changing conditions is precisely what is required for adaptive computer programs. Furthermore, evolution is a massively parallel search method: rather than work on one species at a time, evolution tests and changes millions of species in parallel. Finally, viewed from a high level the rules of evolution are remarkably simple: species evolve by means of random variation (via mutation, recombination, and other operators), followed by natural selection in which the fittest tend to survive and reproduce thus propagating their genetic material to future generations. Yet, these simple rules are thought to be responsible, in large part, for the extraordinary variety and complexity as we see in the biosphere [Mitchell (1998)]. The following sections briefly outline common methods used in the artifical evolution process. More details on these can be found in the excellent book by Greenwood and Tyrrel [Greenwood and Tyrrel (2007)].

#### 1.2.1 Genetic Algorithms: Principles of Natural Selection

Evolution in hardware is very similar to that in nature. However, the one major difference between what happens in nature and what happens in electronics is that the hardware evolution is completely artificial with tunable operation models and heuristics. Hardware evolution is categorized into two major categories based on the evolution style.

- Extrinsic or software evolution.

- Intrinsic or hardware evolution.

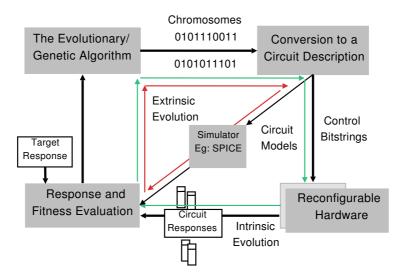

Fig. 1.1: Evolutionary hardware synthesis - Intrinsic and Extrinsic

The two evolutionary synthesis mechanisms are shown in Fig.1.1. The figure shows how a Genetic Algorithm (GA) is used for artificial evolution. After a population generation, the population is varied using mutation/crossover followed by a simulation and evaluation

either in software (extrinsic) or on a reconfigurable platform (extrinsic). The evaluated value of the current solution determines the termination or cycling criterion for the GA.

#### 1.2.2 A Basic GA Cycle

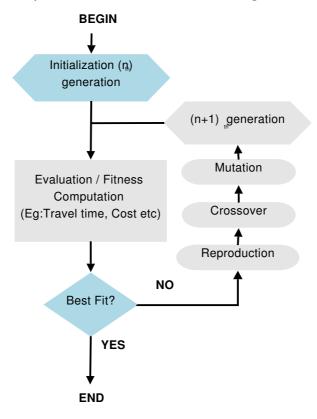

Genetic Algorithms are stochastic algorithms with simple operations like Random number generation, string copy and exchange. They are used for hardware evolution and mimic the process of natural selection to solve difficult problems. GAs fare well with problems having a large search space and their solutions tend to "mature with time". A basic Genetic Algorithm (GA) cycle is demonstrated as a flow algorithm in Fig.1.2. The gene

Fig. 1.2: A basic GA cycle

structure in a GA models the hardware parameters, the on field performance is evaluated as fitness, the structure is varied by crossover and mutation and the fitter chromosomes are chosen for future iterations much like an intelligent biological system. A GA cycle can be summarized using Eq.(1.5).

$$\varphi(n+1) = \zeta(\varepsilon(\upsilon(\varphi(n)))) \tag{1.5}$$

where the variables stand for the initial population generation, population variation, evaluation and selection. The following paragraphs discuss details about each of these operators in a GA cycle.

- 1. Initial Population (IP) Generation ( $\varphi$ )

- 2. Population Variation Crossover and Mutation (v)

- 3. Population Evaluation Fitness ( $\varepsilon$ )

- 4. Selective Progression ( $\zeta$ )

#### **1.2.3** Representation $(\varphi)$

The first major hurdle in modeling a physical problem to be compatible with a genetic algorithm is its representation using a data structure that encodes all the problem parameters. A cue from the biological hierarchy of genetics can be obtained. The genetic hierarchy has a *gene* as its most basic block which has a locus defined in the system. A collection of genes form a *phenotype* which form a part of a *genotype*. The *genome* is a selection of genotypes and constitutes the highest level of hierarchy in the genetic abstraction. There are five common encodings which could be used for population representation.

Integers Consider an RC circuit with the values of R and C to be encoded. The values could be represented using integers - R[470, 220] for [470 $\Omega$ , 220 $\Omega$ ] and C[10, 47] for [10 $\mu$ F, 47 $\mu$ F]

**Binary Strings** The values of the capacitance and resistance above could also be represented using unique binary strings - R[000, 100] for  $[470\Omega, 220\Omega]$  and C[00, 01] for  $[10\mu F, 47\mu F]$

**Real Numbers** Given a l bit binary string, the real number representation can form a compact representation for the same. To translate from a binary representation, in this scheme, a real number x is assigned to a current population model such that  $x \in [x_{min}, x_{max}]$  The encoding scheme is shown in Eq.(1.6). The decoding can be done by substituting  $\tilde{x}$  into Eq.(1.7). This kind of a modeling is often used in assigning tap weights on digital filters

and the popular IEEE 754 standard.

$$\widetilde{x} = \sum_{i=0}^{l-1} b_i \cdot 2^i \quad ; b_i \in \{0, 1\}$$

(1.6)

$$x = x_{min} + \widetilde{x} \cdot \left[ \frac{x_{max} - x_{min}}{2^l - 1} \right]$$

(1.7)

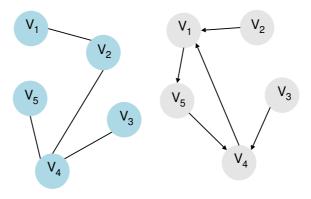

**Graphs** Graphs are another way of IP representation. This scheme is particularly useful in modeling circuit topologies and neural networks. The graphs could be directed or undirected as shown in Fig.1.3 **Hybrids** For the IP representation, hybrid representation

Fig. 1.3: IP representation using directed and undirected graphs

schemes using graphs, real numbers, integers and so on could be used. An example when this is particularly useful is a problem which involves both circuit topologies and component values. Typical design challenges are to identify a proper encoding and IP representation scheme for the problem at hand. A choice of IP modeling can be aptly suited for a specific problem type.

#### **1.2.4** Variation (v)

Variation is the variety inducing process in a given population. This is often a random process which changes the encoded parameters of an IP. The result of a variation operation is the creation of newer offspring which are hopefully better ones. There are two major types of variation operations in the genetic cycle *viz*. mutation and recombination.

**Recombination:** Exemplified below are two types of recombination operations. There could be variations of these or newer ones.

**n-Point Crossover** The n-point crossover mechanism involves the selection of one or more random points (may be heuristic based) in a chromosome representation followed by an interchanging of genetic material among two or more chromosomes Fig.1.2.4.

1 -Point Crossover

2 -Point Crossover

$$1 \ 0 \ 0 \ 1$$

$0 \ 0 \ 1$

$0 \ 0 \ 1$

$0 \ 0 \ 1$

$0 \ 0 \ 1$

$0 \ 0 \ 1$

$0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 0 \ 1$

$0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0 \ 0 \ 0 \ 0$

$0 \ 0$

**Uniform Crossover** This is another popular type of the crossover operation. This the generation of a random selection probability with its cardinality equal to the number of genes in evolving chromosome. A recombination strategy in this involve choosing a gene from the first IP vector if the random selection vector has a probability value  $\geq 0.5$  else from the second IP vector. A new recombination vector is hence produced using the two IP vectors after variation using the selection probability vector as shown exemplified in Fig.1.2.4

#### **1.2.5** Evaluation $(\varepsilon)$

Evaluation is the third major step in the genetic process. In the evaluation step, an objective function  $(\Phi)$  is modeled such that,  $\Phi: X \to \Re$ . Where X is the chromosome under iteration for the given problem. This mapping needs to be a very intelligent one as the final outcome of the GA is strongly dependant on the fitness function. This usually involves the inclusion of all the optimization parameters in the problem. Oftentimes, they are conflicting but some other times they are independent. The objective function  $(\Phi)$  is either maximized or minimized. Depending on this, a given chromosome is selected if  $\Phi(X(n+1)) \geq \Phi(X(n))$  or if  $\Phi(X(n+1)) \leq \Phi(X(n))$ . An example objective function

is shown in Eq.(1.8)

$$\Phi(s) = \frac{1}{\sum_{i=1}^{M} [G'(i) - G(i)]^2 + \epsilon} , \ \epsilon << 1$$

(1.8)

where  $\epsilon$  is used to keep the fraction finite and the denominator of the fitness is the square of the difference of objectives between the current and the past iteration.

#### **1.2.6** Selection ( $\zeta$ )

Selection of a given chromosome from an IP pool to move on to future generations involves problem heuristics and results in maturing solutions and competitive species. Five typical selection schemes are outlined in below.

**Uniform Selection** is a scheme where the chromosomes from a population pool are selected randomly with an equal probability. Of course the convergence rates of this scheme are slow but this provides the highest variety of populace to move on to future generations.

**Fitness Proportional Selection** involves the selection of a chromosome from a pool with a probability proportional to its fitness value as shown in Eq.(1.9)

$$prob(i) = \frac{\Phi_i}{\sum_{j=1}^N \Phi_j}$$

(1.9)

**Fitness Ranking Selection** is similar to fitness proportional selection but the difference being that the selection probability is this case is proportional to the exponential transform of the ranks assigned to chromosomes based on their fitness values, Eq.(1.10)

$$prob(i) = \frac{1 - exp(-r)}{C}$$

$r: rank, C: norm \ const$  (1.10)

**q-Tournament Selection** is a biased selection scheme which involves the selection of a chromosome from a random set of q individuals chosen from the pool of chromosomes under the current iteration Eq.(1.11).

$$\Phi_{max}$$

from Random q individuals. (1.11)

**Truncation Selection** is one of the most popular selection schemes which involves the choice of promoting  $\mu$  offspring with high fitness values among a set of  $(\lambda + \mu)$  individuals as shown in Eq.(1.12)

$$\{\Phi_{high}^1, \Phi_{high}^2 \dots \Phi_{high}^{\mu}\} \ among \ (\lambda + \mu) \ offspring.$$

(1.12)

The methods of IP Generation, Variation, Evaluation and Selection proposed in this section are just an example of the methods currently popular in literature. There are numerous other variations of these. The most important aspect of a GA is the adjustment of these methods based on problem heuristics. In Chap.3 and Chap.4 we exemplify the importance of these heuristic adaptations using two important problems in circuit and systems design. After a genetic approach to optimization, the thesis proposes a reliable system design on a reconfigurable platform in Chap.5. Hence, in the following sections, the thesis presents some basics about reconfigurable hardware, reliability and soft errors.

## 1.3 Reconfigurable Hardware and Reliability

Field Programmable Gate Arrays (FPGAs) are programmable digital logic chips which can be programmed to do almost any digital function.

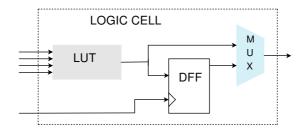

#### 1.3.1 Logic Cell

FPGAs are built from one basic *logic-cell*, duplicated hundreds or thousands of times. A logic-cell is basically a small lookup table (LUT), a D-flipflop and a 2-to-1 MUX (to bypass the flipflop if desired). Fig.1.4 outlines a typical logic cell showing the multiplexer, the flip flop and the LUT. The LUT is like a small RAM and has typically 4 inputs and can implement any logic gate with up to 4-inputs. For example, an AND gate with 3 inputs, whose result is then ORed with another input would fit in one 4-input LUT.

Fig. 1.4: A typical FPGA Logic Cell

#### 1.3.2 Interconnect and Routing

Each logic-cell can be connected to other logic-cells through interconnect resources (wires/muxes placed around the logic-cells). Each cell can do little, but with lots of them connected together, complex logic functions can be created. FPGAs also have fast dedicated lines in between neighboring logic cells. The most common lines are called carry chains. Carry chains allow the creation of arithmetic functions like counters and adders efficiently. Also, within the FPGA fabric, there are interconnect buffers which are tri-stated AND-OR logic elements and can be used to realize hardwired logic functions in special scenarios.

#### 1.3.3 Internal RAM

In addition to logic, all new FPGAs have dedicated blocks of static RAM distributed among and controlled by the logic elements. There are many parameters affecting the RAM operation. The main parameter is the number of agents that can access the RAM simultaneously. Based on the access patterns, they can be classified as

- Single-port RAMs: only one agent can read/write the RAM.

- Dual-port or quad-port RAMs: 2 or 4 agents can read/write.

Dual port RAMs are efficient in getting data across clock domains where each agent can use a different clock.

#### **Blockram vs. Distributed RAM**

There are two types of internal RAMs in an FPGA: blockrams and distributed RAMs. The size of the RAM needed in an application usually determines which type is used.

- 1. The big RAM blocks are blockrams, which are dedicated areas in the FPGA. Each FPGA has a limited number of these and if unused, they are lost (they cannot be used for anything but RAM).

- 2. The small RAM blocks are either in smaller blockrams or in distributed RAM. Distributed RAM allows using the FPGA logic-cells as tiny RAMs.

Distributed RAM brings a lot of flexibility in the RAM distribution in an FPGA, but isn't efficient in term of area as a logic-cell can actually hold very little RAM. There are a large number of block RAMs within the Xilinx family of FPGAs [fpga4fun (2008)]

#### **1.3.4** Errors in High Performance Memories

In the field of high-performance communication memory devices, it is critical for designs to be immune to soft errors or single-event upsets. As device technology scales, the area efficiency of memory devices decreases, and a device's natural resistances against SEUs (single-event upsets) decreases. A reconfigurable platform like an FPGA makes the hardware even more susceptible as device configurations in the FPGA are stored in SRAM cells.

SEUs are random and rarely catastrophic, and they do not normally destroy a device. Many systems can tolerate some level of soft errors. An occasional bad bit may be unnoticeable and unimportant in many applications. However the use of memory elements in mission-critical applications to control system functions makes soft errors more impactive and lead to not only corrupt data, but also a loss of function and system-critical failures. Getting worse, not better. Poor system design is a common source of SEUs. High performance memory devices normally comprise SRAM cells, combinational logic, and latches. In high-performance memories, the area efficiency is usually low. Past research [Lima *et al.* (2003)], [C Carmichael and Caffrey (1999)] shows that combinational logic is less susceptible to soft errors than memory cells because of natural resistances set up by masking. However, these natural resistances could diminish as devices scale and technologies advance[C Carmichael and Caffrey (1999)].

Check information for memories could be used to serve as a correction mechanism for SEUs. They serves two purposes; First, when a check word is read from memory, the check information can help determine whether any of the data bits have changed. In ECC detection, the check information can help determine whether a single bit or more than one bit has changed. Second, if only a single bit has changed, ECC correction helps determine which bit changed and facilitate correcting the data by flipping the bit back to its complementary value. An ECC-detection circuit detecting a change in one or more bits in a word of data is broadly categorized as an ECC error. These errors can further be categorized as functions of the number of bits in the error. ECC circuits described in literature can correct single bits and report multi-bit errors [Mastipuram and Wee (2004)]. These can be implemented for correction in hardware or software. However, the ECC logic designed in hardware is itself SEU prone as the logic for the ECC in a reconfigurable platform would again have to reside in LUTs. The concluding parts of this thesis present insights into the design of a reliable high performance on chip memory using redundant logic elements in FPGAs. This provides a robust and reliable memory for high performance applications with a built in hardwired ECC.

## 1.4 Context and Objective

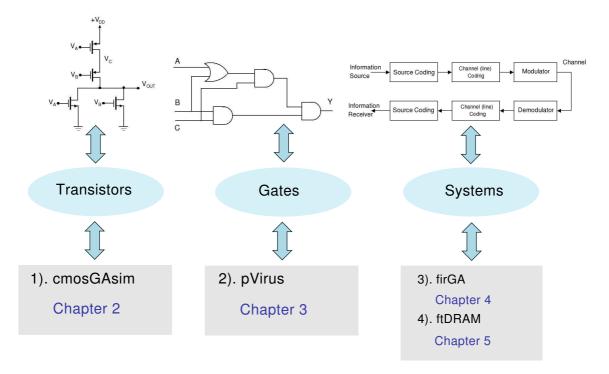

The general framework of this thesis is the design of optimal and reliable systems. For this we use heuristic genetic algorithms and reconfigurable hardware. We look at three problems at three abstraction levels in the first three chapters as shown in Fig.1.5. The problems in the figure are summarized with short code names - cmosGAsim for the second chapter, pVirus for the third, firGA for the fourth and ftDRAM for the fifth. The first problem (cmosGAsim) addresses the issue of obtaining optimal transistor netlists with no redundancy for arbitrary truth table specifications. This leads to what is known as the gateless custom VLSI design flow which may help in designing custom library cells on the fly with digital CMOS logic styles. The second problem (pVirus) is the power virus problem which is an early peak dynamic power estimation problem. This is a critical problem from the perspective of system reliability and design guard-banding. We use a heuristic GA and vector partitioning methods for the PDPE problem. The third optimization problem (firGA) works at the system level describing the design of optimal filters automatically which are reliable and robust using a novel, heuristic GA. The final prob-

lem addressed by the thesis is that of the reliability and efficient design of high speed memories (ftDRAM). We use a reconfigurable platform (FPGAs) for demonstrating the same. Hence, in the context of reliability and optimality of system designs, this thesis contributes significantly by providing new insights into important issues. The major ob-

Fig. 1.5: The thesis framework - optimization abstractions

jectives of the thesis are to show new methods for optimization and design of reliable systems. This is effected using a reconfigurable platform as well as other grounds. Besides this the thesis also intends to point out the importance of the various steps in genetic optimization for a given problem. The thesis also aims to bring out the effective use of design abstraction, layout tools, simulation software and the genetic methods in heuristic scenarios. It aims to show that the performance of systems can be enhanced by intelligent design choices and systems can be made reliable using redundant logic elements in a hardware platform.

#### 1.5 Organization of Thesis

To address the optimization problems, the thesis follows an *abstraction* organization, *i.e* it work on optimization problems at the transistor level and move upto the system level. Reliable and adaptive systems being at the core of all this. The thesis is organized as follows

- Ch.2 Genetic transistor level optimization: A genetic approach to gateless custom VLSI design flow Problem showing the usage of GAs to obtain optimal transistor netlists directly from truth table descriptions.

- Ch.3 **Genetic gate level optimization:** Vector parts and genetic search methods for PDPE in digital circuits Problem of reliable early power estimates for effective guard-banding and optimal system synthesis.

- Ch.4 Genetic system level optimization: Hardware based genetic evolution of FIR filters Problem of designing Self-adaptive and reliably responsive filters for arbitrary frequency responses.

- Ch.5 System level Reconfigurable Design: A SEU tolerant distributed CLB RAM for in-circuit reconfiguration - Problem of designing reliable memories on reconfigurable platforms.

- App. CMOS Concepts, PDPE Results and ECC: The three appendices at the end of the thesis describe basics of CMOS logic design, Hamming ECC and the PDPE results on ISCAS'85 benchmark circuits using the proposed techniques.

#### **CHAPTER 2**

## A GENETIC APPROACH TO GATELESS CUSTOM VLSI DESIGN FLOW

## 2.1 Introduction and Background

Automation in modern microelectronics has resulted in multiple methods for the design and optimization of digital circuits. These automated methods incorporate gate level optimizations followed by the use of standard library cells to map the designs to hardware. In several custom designed Integrated Circuits (ICs), the use of standard libraries translates to hardware redundancy. This is because, standard library cells, due to their limitations in size and number, often result in having several unused transistors for the custom logic. Consequently, the use of tailored cells for specific applications become necessary. Application specific generation of such cells utilizes on-chip hardware effectively besides providing fast and flexible designs operating with lesser redundancy and better performance.

Realization of custom circuits - cells or blocks, involve three implementation phases as described in [Lefebvre and Marple (1997)]:

- Creation of transistor circuit topologies which provide a specific digital function.

- Sizing and ordering of the transistors in the circuit topology.

- Placing, routing and compacting the transistors in layout.

Each of the above stages involve trade-offs which must be optimized across all stages. This chapter proposes to address the first phase of transistor circuit topology creation, automatically.

In literature, much attention has been given to the sizing [Rogenmoser *et al.* (1996)], [Heusler and Fichtner (1991)] and placing of transistors [Lefebvre and Marple (1997)],

[Ho et al. (1997)] and [Bahuman et al. (2002)] in custom and semi-custom circuits. Using Genetic Algorithms (GAs) in [Ho et al. (1997)], Murphy, et. al, describe the placement optimization of a cell followed by the extraction of the netlist. They employ sigmoidal transistor characteristics for an Artifical Neural Network (ANN) model unlike the switch characteristics in our case. Their major aim is the use of primitive components and reduction of the parasitic capacitance rather than a topological optimization. In [Bahuman et al. (2002)] is described a GADO model for a custom cell. But their starting point is the placement optimization unlike configuration optimization as in our case.

This chapter focuses on the direct transistor netlist generation using Genetic Algorithms for optimization. Genetic methods have been applied in the past for gate level synthesis [Hounsell and Arslan (2000)] besides specific optimization methods for Pass Transistor Logic (PTL) [Cho and Lee], Complementary PTL (CPL) [Yano *et al.* (1990)], Differential PTL (DPTL) [Pasternak (1993)], Double PTL (DPL) [Suzuki *et al.* (1993)] and other non-complementary MOS logic styles. Mazumder and Rudnick, in [Mazumder and Rudnick (1999)] provide a good insight into the problems in VLSI design and synthesis techniques.

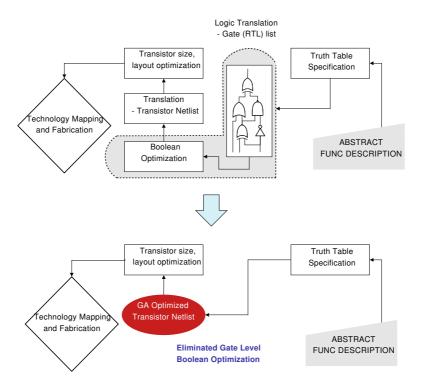

The methods we use in this chapter involve the use of Genetic Operators to evolve transistor netlists for a certain functional requirement described by an input truth table. The netlist generation, because of the characteristics of the genetic operators, inherits direct optimization at the transistor level. This gives an optimized transistor netlist which would otherwise be derived after converting the truth table to its min-terms and then applying the Boolean simplification operations. In the latter case, the netlist obtained would still not be optimized to exploit internal topological optimizations of the transistors. The main contribution of this work is to propose the genetic methodology of direct evolution for the transistor netlist from functional descriptions of circuits. The chapter also provides a methodology for incorporating a gateless optimization algorithm in the custom circuit design flow to provide the creation of custom library cells *in-situ* as shown in Fig. 2.1. This favorably enhances the performance of custom circuit syntheses and provides better utilization of transistor resources besides automation and simplification of the design flow, by eliminating the boolean optimization step.

Fig. 2.1: Custom design flow simplification using the proposed genetic method: The genetic flow eliminates the intermediate Boolean simplification step from the normal gate optimized flow by providing a direct transistor optimized netlist, ready for size/layout tuning in custom circuits.

Although described in an earlier chapter, we reiterate the basic concepts of Genetic Algorithms [Godlberg (1989)] necessary to understand the rest of the chapter.

Genetic algorithms work on a set of *chromosomes/genotypes* called the population. Each chromosome represents a solution to the problem which is associated with a *fitness* value that reflects how good it is compared to the other solutions in the population. The variation process comprises of *crossover* and *mutation*, which concoct material by partial exchange among *genotypes* and by random alterations of data strings. The frequency of these operations is controlled by certain pre-set probabilities which require heuristics appropriate for the particular problem at hand. The *representation*, *variation*, *evaluation* and *selection* operations constitute the basic GA cycle or *generation*.

Table 2.1: Gene structure in a chromosome using .sim encoding <sup>a</sup>

| $T_{ij}$       | $S_{ij}$           | $n^1_{ij}$                               | $n_{ij}^2$                | $W_{ij}$ | $L_{ij}$ | $f_i$ | $\delta_{ij}$ |

|----------------|--------------------|------------------------------------------|---------------------------|----------|----------|-------|---------------|

| $\overline{p}$ | CLK                | $V_{dd}$                                 | 1                         | 4        | 2        |       |               |

| n              | $R_{ij}(A_1A_N)$   | 1                                        | $R_{ij}(2\overline{N+1})$ | 4        | 2        |       |               |

| n              | $R_{ij+1}(A_1A_N)$ | $R_{ij+1}(S_{ik}S_{ij-1})$               | $R_{ij}(2\overline{N+1})$ | 4        | 2        |       |               |

| •              | •                  | •                                        | •                         | •        | •        |       |               |

| •              | •                  | . 10 10                                  | •                         | •        | •        |       |               |

| n              | CLK                | $max[n_{ij}^{1,2} \dots n_{ij+N}^{1,2}]$ | gnd                       | 4        | 2        | $f_i$ | $\delta_{ij}$ |

$a \quad T_{ij} \colon \text{Transistor type, } S_{ij} \colon \text{Transistor gate node, } W_{ij} \colon \text{Transistor width in } \mu m, L_{ij} \colon \text{Length in } \mu m, N \colon \text{Number of Inputs, } R_{ij} \colon \text{Uniform Random Selector}$

## 2.2 Genetic Topological Synthesis

#### 2.2.1 Representation and initial population

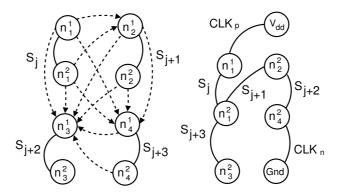

Gene representation in the Allele: Representation of the genes for evolution is a critical choice to keep the circuit topology valid and provide faster convergence. Eq. (2.1) shows the chosen representation. The representation follows in line with the genetic ideology and the IRSIM simulator codes as described in Appendix.A. A thorough understanding of the material Appendix.A is highly recommended before proceeding. Each transistor is represented as a triplet  $\langle S_j, n_j^1, n_j^2 \rangle$ , where  $S_j$  stands for the node to which the input signal and the gate of the  $j^{th}$  transistor are connected.  $n_j^1$  and  $n_j^2$  are the nodes to which the source and drain of the  $j^{th}$  transistor are connected Section.A.2 in Appendix.A. A chromosome is a sequence of such triplets which are equal in number to the input signals determined from the truth table. These form netlist inputs to the IRSIM simulator for fitness evaluation and selection. A subsequence of these signal triplets can be used for mapping the inputs (or transistor gates) to one of the variables  $A_1, A_2 \dots A_N$ . In other words, the  $S_j$  values of the triplets in the subsequence shall be a one-one mapping from among  $A_i$ 's,  $0 \le i \le N$ .

Gene Structure: The internal gene structure of a chromosome is shown in Table. 2.1. The representation using a *Perl parser* is designed to conform to the spice netlist. This can be directly used for evaluation, using the *IRSIM* switch level simulator.

$$\left[ S_j \ n_j^1 \ n_j^2 \ \middle| S_{j+1} \ n_{j+1}^1 \ n_{j+1}^2 \ \middle| \dots \dots \ \middle| S_{j+N-1} \ n_{j+N-1}^1 \ n_{j+N-1}^2 \right]$$

(2.1)

The methodology for the generation of the **initial population** is shown in Fig. 2.2 and

Fig. 2.2: Initial population generation with the corresponding transistor topology and SFG for the netlist. The dotted lines contribute to the random node choice for the next chromosome. The final obtained netlist is functionally valid.

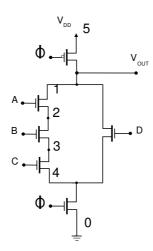

Table 2.2: A model .sim file for the circuit example in Fig.2.3

| line | text                  |                |        |       |          |                   |  |  |

|------|-----------------------|----------------|--------|-------|----------|-------------------|--|--|

| 1    | units: 100 tech: cmos |                |        |       |          |                   |  |  |

| 2    | type                  | gate           | source | drain | length   | width             |  |  |

| 3    | p                     | $\phi$         | 5      | 1     | $L_{51}$ | $\mathbf{W}_{51}$ |  |  |

| 4    | n                     | $\phi$         | 4      | 0     | $L_{40}$ | $\mathrm{W}_{40}$ |  |  |

| 5    |                       |                |        |       |          |                   |  |  |

| 6    | n                     | $V_A$          | 1      | 2     | $L_{12}$ | $\mathbf{W}_{12}$ |  |  |

| 7    | n                     | $\mathbf{V}_B$ | 2      | 3     | $L_{23}$ | $\mathbf{W}_{23}$ |  |  |